5. Projekt topografii układu.

5.1.1. Charakterystyka ogólna.

Mając zakończony etap tworzenia schematu funkcjonalnego i jego weryfikacje możemy przejść do fazy projektowania topografii. Jest to etap mający największy wpływ na końcowe osiągi układu (szybkość, zużycie energii, powierzchnia, itp.). Jest to spowodowane bezpośrednim wpływem zaprojektowanego rozkładu elementów z uwzględnieniem własności fizycznych półprzewodników na transkonduktancję tranzystorów, pojemności pasożytnicze i rezystancje.

5.1.2. Oprogramowanie pomocne przy tworzeniu topografii.

Wraz ze wzrostem wielkości

i złożoności tworzonych topografii konieczne jest zastosowanie programów

ułatwiających rysowanie masek oraz sprawdzających poprawność reguł projektowych.

Programem takim może być UNCLE. Szerszy opis możliwości programu można

znaleźć tutaj.

Cechy programu pomocne przy tworzeniu topografii:

Program UNCLE zapewnia nam ciągłe sprawdzanie reguł projektowania, jednak dobrze jest ograniczyć obszar podlegający sprawdzaniu, gdyż zmniejsza to czas obliczeń. Ważnym czynnikiem wpływającym na szybkość sprawdzania jest wybór technologii układu (czyli ilość reguł jakie muszą być sprawdzone).

Wiele problemów pojawiających się wraz z postępem prac przy tworzeniu topografii można ominąć dzięki stworzeniu wstępnej struktury układu przy użyciu notacji symbolicznej. Projektant będzie mógł skoncentrować się na odpowiednim ułożeniu elementów - pogrupować elementy w jednakowe zespoły z możliwością ich późniejszego wykorzystania (kopiowania). Nie bez znaczenia jest także liczba połączeń globalnych - ich ilość między grupami powinna być ograniczona do minimum, a ścieżki możliwie najkrótsze. Jest to spowodowane właściwościami fizycznymi warstw wchodzących w skład układu.

Projektowanie masek należy rozpocząć od wyboru technologii wykonania układu scalonego. Wybór technologii określa między innymi minimalny rozmiar tranzystora. UNCLE umożliwia wykorzystanie tzw. pliku technologicznego do ułatwienia rysowania poszczególnych elementów. W pliku są zawarte kombinacje masek, które można wykorzystać do tworzenia pojedynczych obszarów projektowanego układu. Na przykład, rysując obszar N nie będziemy za każdym razem deklarować trzech masek - posiadamy obszar N określony w pliku technologicznym.

W celu uzyskania optymalnego schematu układu możemy posłużyć się metodami służącymi do optymalizacji. Jedna z metod jest reprezentacja układu w postaci grafu i użycie metody Eulera. Po wykonaniu czynności związanych z określeniem wstępnego schematu topologii możemy przejść do rysowania topologii. Czynność ta może być wielokrotnie powtarzana (np. zbyt długie połączenia) tak, aby spełnić wszelkie oczekiwania związane z projektowanym układem. Oczywiście, wejściowy schemat topologii nie powinien zostać zbytnio zniekształcony.

5.1.7. Dalsze etapy tworzenia topografii.

Na tym etapie mamy przygotowaną topografię układu, którą możemy poddać ekstrakcji. Rezultatem procesu jest plik (tzw. netlista) służący do przeprowadzenia symulacji układu. Symulację można przeprowadzić np. programem PSPICE lub SMASH. Symulacja pozwala na sprawdzenie faktycznych parametrów naszego układu, np. czy nie powstały pasożytnicze tranzystory na wskutek zbyt blisko położonych diód. Jeśli parametry okażą się niezadawalające (np. czasy narastania sygnału) z wcześniejszymi założeniami dotyczącymi układu, to musimy powrócić do fazy szacowania parametrów lub tworzenia struktury. Modyfikacje zapewne będą się koncentrować wokół współczynnika długość/szerokość. Ten współczynnik wpływa na transkonduktancję oraz wartości pojemności pasożytniczych źródło/dren. Oczywiście projektant może zdecydować się na przebudowę schematu całej topologii lub jej części tak, aby uzyskać pożądane rezultaty.

Wymiary fizyczne elementów (np. tranzystory) oraz ich wzajemne położenie wykonanych w technice VLSI maja znaczący wpływ na ich parametry elektryczne. Są to przede wszystkim pojemności pasożytnicze oraz rezystancje i indukcyjności pasożytnicze. Ww. wielkości pasożytnicze stanowią duże źródło problemów, dlatego należy wykonać projekt układu z ich uwzględnieniem. W pierwszej kolejności należy dobrać parametry geometryczne tranzystorów tak, aby spełniały założenia odnośnie parametrów statycznych. Następnie projektujemy topografię i wykonujemy symulację komputerową, która zweryfikuje parametry dynamiczne elementów.

W przypadku korzystania z

elementów logicznych należy określić parametry statyczne i dynamiczne tych

elementów (najczęściej bramek logicznych). Należy założyć wymiary fizyczne

tranzystorów, które określą parametry charakterystyczne tranzystorów w

wybranej technologii. Wykonując analizę dynamiczną należy obliczyć pojemności

pasożytnicze. Zaliczamy do nich np. pojemność drenu względem podłoża tranzystora,

pojemności wyjściowe czy też pojemności linii łączących. Dysponując pojemności

pasożytniczymi możemy przystąpić do obliczania czasów narastania i opadania

sygnału wyjściowego bramki.

Przechodząc przez omówione

powyżej kroki uzyskujemy charakterystyki przejściowe oraz maksymalną częstotliwość

przełączania. Poddając analizie obliczone wartości możemy zdecydować się

na powtórną zmianę wymiarów geometrycznych tranzystorów, aby wartości były

poprawne.

5.3. Wybór technologii i reguły.

Przed przystąpieniem do tworzenia topologii należy zdecydować się na sposób fabrykacji, który będzie użyty przy wytworzeniu produktu. Wybór technologii decyduje o końcowych parametrach układu oraz o kosztach jego wytworzenia. Istnieją typy układów, dla których najlepsza jest dana technologia. W programie UNCLE najczęściej wybieramy przygotowane technologie.

UNCLE zapewnia bieżąca kontrolę reguł projektowania. Należy określić obszar, który będzie podlegał weryfikacji. Ma to na celu ograniczenie czasu pochłanianego przez kontrolę. W naszym przypadku będziemy posługiwali się regułami typowymi dla podejścia skalowanego (lambda-rules), ponieważ pozwala w dogodny sposób zdefiniować technologie wraz z jej ograniczeniami.

Przykład reguł projektowych dla CMOS:

5.4. Zdefiniowanie elementów bazowych i nanoszenie warstw.

Po zdefiniowaniu technologii możemy przystąpić do rysowania topologii przy pomocy programu UNCLE. W naszym przypadku będzie to projekt topologii prostego sumatora. Wykonanie symbolicznego schematu, jego optymalizacja oraz stworzenie topografii - taka kolejność pozwala zaoszczędzić czas projektowania oraz uchronić się przed błędami mogącymi wystąpić w późniejszych etapach.

Zwykle w układzie elektrycznym większość elementów jest powtarzanych. Tak też jest w sumatorze i powinno zostać wykorzystane przez projektanta do stworzenia topologii o hierarchicznej budowie. Używając UNCLE możemy to zrealizować przez wykorzystanie mechanizmu komórek (cell). Wyróżniamy więc podstawowe funkcje logiczne jak iloczyn czy suma, następnie projektujemy dla każdej z funkcji sieć tranzystorów i umieszczamy ją w jednej komórce. Każda komórka posiada swoją referencję - będziemy ją mogli wykorzystać wielokrotnie przy rysowaniu głównej sieci sumatora. Dla większego ułatwienia projektowania, UNCLE umożliwia zagnieżdżanie komórek, co prowadzi do powstania hierarchii. Wielokrotnie wykonywanymi operacjami przy tworzeniu topologii z wykorzystaniem UNCLE będą:

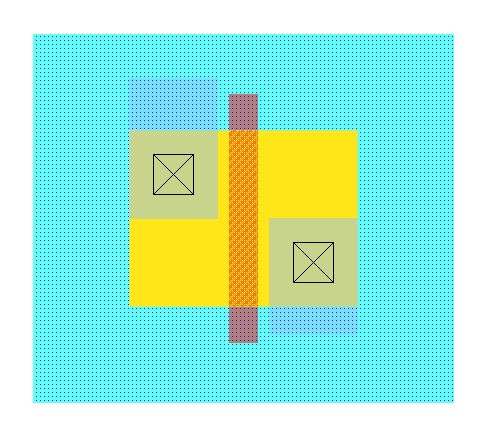

W pierwszej kolejności zgodnie z przedstawionymi operacjami i zasadami tworzymy tranzystory. Oczywiście, jeśli są zdefiniowane standardowo, to możemy używając ich przejść do tworzenia funkcji logicznych.

Jeśli założymy, że chodzi

nam o zachowanie jak najmniejszych rozmiarów to określając poszczególne

obszary dojdziemy do właściwego kształtu tranzystora. Rozpoczynając od

szerokości aktywnego obszaru - będzie on ograniczony przez minimalny obszar

kontaktu (diffusion contact - jest konieczny do połączenia źródła i drenu)

oraz minimalny obszar separacji miedzy obszarem kontaktu a aktywnymi obszarami.

Podobnie będzie z bramką tranzystora, która przyjmie minimalną szerokość.

Mając powyższe założenia będziemy mogli ograniczyć całkowitą długość aktywnego

obszaru. Rozważając tranzystor typu p musimy umieścić w nim obszary n-well

(n-well obszar umożliwiający stworzenie n+ w obszarze p), którego minimalna

wielkość będzie ograniczona przez aktywny obszar tego tranzystora. Nie

bez znaczenia jest także obszar między tranzystorami typu n i p., który

ograniczony jest przez konieczność separacji obszarów aktywnego obszaru

(n+ active area) i podstawy tranzystora (n-well).

Jeśli nie korzystamy z bibliotecznych tranzystorów

to niezbędną czynnością jest ekstrakcja układu tranzystora do formatu czytelnego

dla programu PSPICE lub SMASH i jego symulacja.

Projektowanie podstawowych funkcji logicznych będzie polegać na zaprojektowaniu sieci tranzystorów. Po narysowaniu odpowiednich elementów musi nastąpić ich ekstrakcja i weryfikacja.

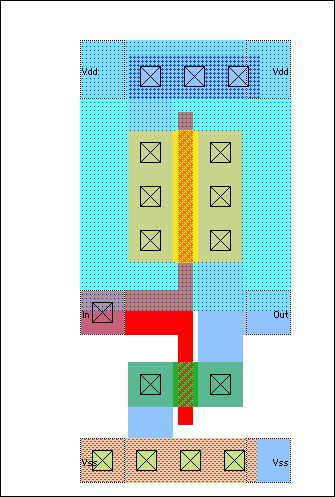

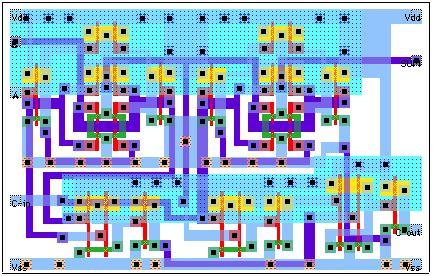

5.4.4. Realizacja całości układu.

Proces projektowania całości układu jest bardzo podobny do tworzenia funkcji logicznych. Jednak zamiast sieci tranzystorów dysponujemy siecią logicznych bramek końcowego układu. W procesie projektowania będziemy korzystać ze sprawdzonych funkcji zrealizowanych wcześniej (suma, iloczyn). Poniższe rysunki przedstawiają kolejne etapy.

Po zaprojektowaniu całej topologii należy zweryfikować jej poprawność. Będą to analogiczne czynności jak przy weryfikacji funkcji logicznych (ekstrakcja, symulacja).

5.5. Metody wspomaganie projektowanie topografii.

5.5.1 Optymalizacja rozmieszczenia elementów.

Poniżej przedstawiony jest układ dla którego należy stworzyć projekt topografii.

W pierwszym etapie, bez stosowania reguł grafowych można wybrać arbitralny schemat topologii (kolejność bramek polikrzemowych). Jednak jak widać na rysunku A, w takim przypadku odstęp musi być na tyle duży aby można było zrealizować połączenie dla dwóch kontaktów metalowych (metal-diffusion contact) i jednego odstępu dyfuzja-dyfuzja. Oczywiście wiąże się to ze zwiększeniem obszaru, na którym może być zrealizowany układ.

Tak nieoszczędną sytuację można rozwiązać poprzez zastosowania metody Eulera do znalezienia optymalnej ścieżki. Tworzymy dwa grafy dla sieci nMOS i pMOS o takiej samej kolejności wejść. Następnie szukamy w nich takiej samej ścieżki, która przechodzi przez wszystkie wierzchołki grafu tylko jeden raz. Obrazowo przedstawione jest to na rysunku B.

W opisywanym przypadku szczęśliwie otrzymaliśmy ścieżkę (E-D-A-B-C) zawarta w każdym z grafów. Rysunek C obrazuje korzyści otrzymane po zastosowaniu metody wyszukiwania ścieżki Eulera.

Jednak najczęściej nie jest możliwe utworzenie ścieżki Eulera obejmujące cały układ. Dlatego też należy poszukiwać ścieżek, które powinny być możliwie najdłuższe.

5.5.2. Znajdowanie najkorzystniejszych połączeń.

Typowymi metodami do wytyczania połączeń przy projektowaniu topografii są: metoda chodzenia labiryntem i metoda przeszukiwania liniowego.

5.5.2.1. Chodzenie labiryntem.

W metodzie tej powierzchnie całkowitą dzielimy na jednakowe kwadraty (prostokąty) i wpisujemy w każdy z nich drogę (ilość kwadratów) jakie musimy przebyć pokonując przeszkody przemieszczając się np. z punktu A do B. Ponieważ jednak rozmiar całkowitej powierzchni zazwyczaj jest duży, to metoda ta jest mało skuteczna. Najczęściej jest ona składową innej metody.

5.5.2.2. Przeszukiwanie liniowe.

Metoda ta jest szybsza i nie zabiera tak dużo pamięci przy obliczeniach jak metoda chodzenia labiryntem. Polega ona na prowadzeniu linii poziomych i pionowych przy omijaniu przeszkód tak aby osiągnąć punkt końcowy przebywając drogę o jak najkrótszej długości. Zwykle niewielka procentowo ilość dróg jest wadliwa.

Maski wykorzystane w procesie fabrykacji musza spełniać reguły projektowe. Zasady te dotyczą geometrycznych wymiarów decydujących o właściwościach elementów. Na przykład, jeśli linia metalu jest zbyt cienka to może zostać zniszczona w procesie fabrykacji lub zostać przepalona podczas użytkowania układu. Podobnie jest z liniami zbyt blisko siebie - mogą połączyć się w procesie fabrykacji. Zatem celem reguł jest uzyskanie jak najmniejszych wymiarów przy zachowaniu poprawności działania układu.

Reguły projektowe opisane są zazwyczaj za pomocą dwóch podejść :

Przykładowe zasady dla tech. MOSIS.

| Numer zasady | Opis | L-zasada (L-Rule) |

| R1 | Minimum active area width | 3 L |

| R2 | Minimum active area spacing | 3 L |

| R3 | Minimum poly width | 2 L |

| R4 | Minimum poly spacing | 2 L |

| R5 | Minimum gate extension of poly over active | 2 L |

| R6 | Minimum poly-active edge spacing (poly outside active area) | 1 L |

| R7 | Minimum poly-active edge spacing (poly inside active area) | 3 L |

| R8 | Minimum metal width | 3 L |

| R9 | Minimum metal spacing | 3 L |

| R10 | Poly contact size | 2 L |

| R11 | Minimum poly contact spacing | 2 L |

| R12 | Minimum poly contact to poly edge spacing | 1 L |

| R13 | Minimum poly contact to metal edge spacing | 1 L |

| R14 | Minimum poly contact to active edge spacing | 3 L |

| R15 | Active contact size | 2 L |

| R16 | Minimum active contact spacing (on the same active region) | 2 L |

| R17 | Minimum active contact to active edge spacing | 1 L |

| R18 | Minimum active contact to metal edge spacing | 1 L |

| R19 | Minimum active contact to poly edge spacing | 3 L |

| R20 | Minimum active contact spacing (on different active regions) | 6 L |